REALISATION MATERIELLE D'UNE CHAINE

INTEGREE DE CODAGE CANAL (CODEUR

REED-SOLOMON - TRANSCODAGE PCM - CODEUR CONVOLUTIONNEL)

BANC DE SIMULATION D'UNE TRANSMISSION CODEE

Catherine LAMBERT

Jean-Pierre ROCHER

ENSEEIHT/GAPSE 2 rue Camichel 31071 TOULOUSE CEDEX

CNES 18 avenue Ed. Belin 31055 TOULOUSE CEDEX

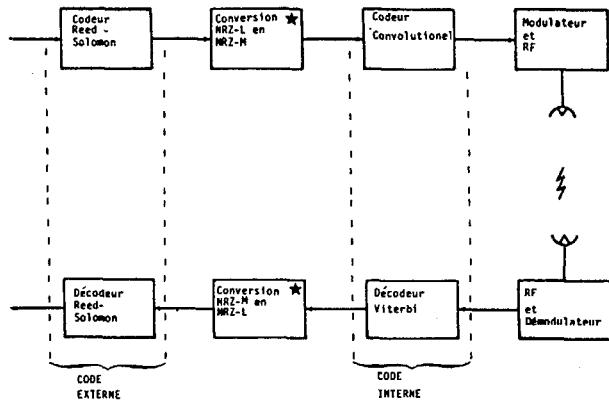

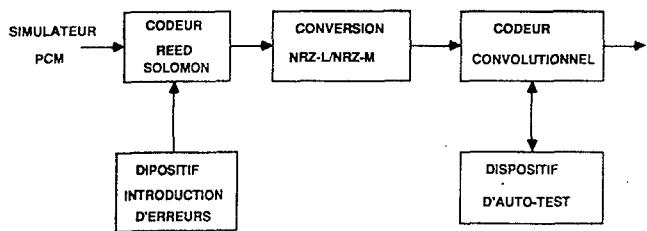

Cet article décrit dans le cadre de la standardisation internationale des systèmes de données spatiales, la mise en œuvre matérielle de codes complexes, en temps réel et pour des débits élevés (au delà de 1Mbit/s). La chaîne de codage canal réalisée comprend un codeur Reed-Solomon (255,223), un transcodage NRZ, un codeur convolutionnel (7,1/2) et un dispositif d'introduction d'erreur à la sortie du train de bits codé Reed-Solomon. Nous présentons l'algorithme utilisé pour chacune de ces réalisations. Cette chaîne mise à disposition des utilisateurs simule le codage effectué à bord des véhicules spatiaux et permet de vérifier le bon fonctionnement des décodeurs utilisés au sol.

In the field of international standardization for space data systems, we show in this paper that putting complex codes into practice is possible in real time and for high data rates (more than 1Mbit/s). This coding system is composed of a Reed-Solomon encoder (255,223), a NRZ-M encoder, a convolutional encoder (7,1/2) and a device in order to introduce errors in Reed-Solomon codeblocks. We give an algorithm for each of these material realizations. This system, which is used on ground bases and which simulates the on-board encoding systems will permit to check ground decoders.

## 1. INTRODUCTION

Le CNES, membre du CCSDS ("Consultative Committee for Space Data Systems") contribue par son action à l'élaboration de recommandations internationales portant sur l'ensemble des données spatiales en vue de permettre l'interopérabilité des futurs systèmes spatiaux et de faciliter les échanges de données ainsi que les services entre agences. Le CCSDS s'est récemment penché sur le problème du codage dans la transmission de télémesures par paquets, son étude a débouché sur un ensemble de recommandations [1]. Un algorithme de codage préconisé y est décrit : il s'agit d'un codage concaténé de type convolutionnel (7,1/2) et Reed-Solomon (255,223).

Il est essentiel de mettre à disposition des utilisateurs sol une chaîne de codage simulant celle embarquée à bord des véhicules spatiaux et permettant de vérifier le bon fonctionnement des décodeurs. La mise en application des codes très puissants que sont le convolutionnel (7,1/2) et le Reed-Solomon (255,223) à des cadences au delà du 1Mbit/s exige la mise en œuvre de solutions par matériel.

Un critère de rapidité de codage nous a incité à étudier une architecture matérielle originale capable de répondre à nos besoins. La chaîne de codage, dont l'article fait l'objet, se situe en aval d'un simulateur PCM délivrant un train de bits série NRZ-L. Elle est constituée d'un codeur de Reed-Solomon (255, 223), d'une conversion NRZ-M, d'un codeur convolutionnel (7,1/2) et d'un dispositif d'introduction d'erreur après codage Reed-Solomon.

## 2. CODEUR DE REED-SOLOMON (255,223)

Le code de Reed-Solomon (N,K) est un code de bloc caractérisé par les paramètres suivants :

- J = 8 bits par symbole

- N = 2<sup>j</sup> - 1 nombre total de symboles par mot de code RS

- E = capacité de correction d'erreurs de symbole

- 2E = nombre de symboles de contrôle (ou parité R-S)

- K = N - 2E = nombre de symboles d'information

- I = profondeur d'entrelacement.

Le code recommandé par le CCSDS étant le code RS (255,223), chaque élément de son alphabet de codage est un des 256 éléments d'un espace fini, le corps GF (2<sup>8</sup>). Le générateur  $\alpha$  des éléments différents de zéro du corps GF (2<sup>8</sup>), est une racine du polynôme primitif  $f(x) = x^8 + x^7 + x^2 + x + 1$ ; chaque élément non nul de GF (2<sup>8</sup>) peut s'écrire sous la forme d'une puissance entière de  $\alpha$  et donc puisque  $\alpha^8 = \alpha^7 + \alpha^2 + \alpha + 1$  sous la forme d'un polynôme en  $\alpha$  sur GF(2) de degré inférieur à 8 [3]  $\alpha^n = u_7\alpha^7 + u_6\alpha^6 + \dots + u_0 \quad u_i = 0 \text{ ou } 1$

Le code RS(255,223) est capable de corriger jusqu'à 16 symboles dans chaque "mot de code" soit un maximum de 16 x 8 bits.

Le mécanisme d'entrelacement permet d'améliorer la puissance de correction du code : l'entrelacement des symboles d'une profondeur de I aboutit à un code RS (nI, kI) héritant ses propriétés du code RS(n,k), les octets d'un même mot de code RS(n,k) étant séparés par (I-1) octets appartenant aux (I-1) autres codes RS (n,k) [8]. Deux profondeurs d'entrelacement sont recommandées par le CCSDS (I=1 et I=5). Une profondeur de I=5 apporte un gain de performance virtuellement équivalent à une profondeur infinie [2]. Notre réalisation offre à l'utilisateur le choix de la profondeur I (1 < I < 8).

Le codage s'effectue comme celui d'un code cyclique par le calcul du reste d'une division par le polynôme générateur  $g(x)$ . Le codage de Reed-Solomon (255,223) doit être réalisé sur des blocs de données de longueur appropriée :

223 x 8 bits dans le cas où il n'y a pas d'entrelacement (I = 1)

223 x 8 bits x I dans le cas d'un entrelacement de profondeur I.

Le polynôme générateur de degré 32 choisi par le CCSDS est un polynôme palindrome unitaire ce qui facilite la réalisation matérielle

$$g(x) = \sum_{i=0}^{32} G_i x^i$$

avec  $G_0 = G_{32} = 1 = \alpha^0$

1 < I < 16     $G_i = G_{32-i}$

Les coefficients de x (pour le diviseur, le dividende, le quotient et le reste) sont des symboles de 8 bits écrits dans la base  $\alpha^i$ .

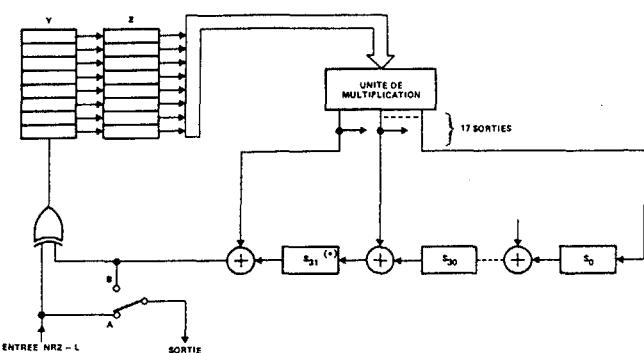

L'algorithme utilisé pour l'implémentation du codeur Reed-Solomon (255,223) avec possibilité d'entrelacement est nouveau dans la mesure où l'architecture de BERLEKAMP [7] est remplacée par un système de pré-multiplication.

Par intervalles de temps fixés, la représentation d'un élément z du corps, dans la base  $\alpha^i$ , est stockée dans le registre Z. L'unité de multiplication a pour entrées les contenus du registre Z, elle doit faire la multiplication série bit par bit de  $G_{31}, G_{30}, \dots, G_0$  par z dans GF(2<sup>8</sup>). Puisque  $G_{32-i} = G_i$  pour  $1 \leq i \leq 16$ , il suffit d'avoir en sortie de l'unité de multiplication le résultat des produits  $zG_0, zG_1, \dots, zG_{16}$  dans la base  $\alpha^i$ .

Soient  $z_0^1, z_1^1, z_2^1, \dots, z_8^1$  les 8 composantes de  $zG_1$  ( $0 \leq i \leq 31$ ),  $z_i^1$  est introduit dans le registre S0 tandis que  $z_1^2, z_2^2, \dots, z_i^2$  et  $z_i^3$  sont simultanément ajoutés grâce à des "ou exclusif" au bit émanant respectivement du registre S1, S2, ..., S31 (décalage vers la gauche). Chaque registre  $S_i$ , mis à part  $S_{31}$ , a une longueur de  $8 \times I$  bits afin de permettre une profondeur d'entrelacement de I ( $1 \leq I \leq 8$ ). Le registre  $S_{31}$  a une longueur de  $8 \times (I-1)$  bits (il n'existe qu'en cas d'entrelacement I = 1). L'entrée du registre Y est reliée à la sortie du "ou exclusif" bit à bit entre les bits composant le symbole d'information et ceux composant le symbole qui sort du registre  $S_{31}$ . Après le calcul des produits  $sG_1$ , le registre Z est donc recharge avec les contenus du registre Y. Lorsque le dernier symbole d'information a été introduit, l'interrupteur est placé en B et les I familles de 32 symboles de contrôle sont alors délivrés bit par bit tandis que les registres Y, Z et  $S_i$  sont mis à zéro.

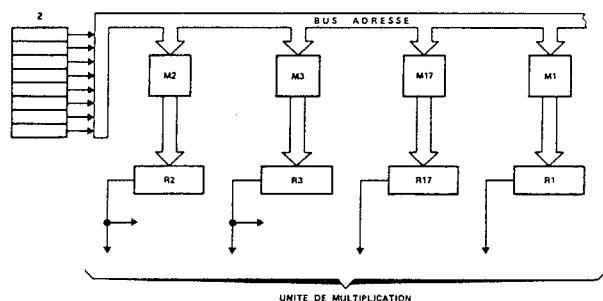

Le calcul effectué dans l'unité de multiplication est réalisé à l'aide de 16 mémoires PROM de 255 x 8 bits. Chacune d'elles est associée à l'un des 16 coefficients de  $g(x)$  : à la mémoire M<sub>l+1</sub> correspond le coefficient G<sub>l</sub> ( $0 \leq l \leq 16$ ). La programmation de ces PROM's a été faite de sorte que les 8 bits de sortie de la mémoire G<sub>l</sub> correspondent au produit Z.G<sub>l</sub> (exprimé dans  $\alpha^i$ ) si l'adresse présente à l'entrée de la mémoire est z (exprimé dans  $\alpha^i$ ).

### 3. CONVERSION DE MODULATION NRZ-L en NRZ-M

La télémétrie PCM-Pulse Code Modulation représente la classe la plus utilisée de télémétries numériques.

Le CCSDS préconise l'utilisation de la modulation NRZ-L et NRZ-M pour des liaisons avec suppression de porteuse. Les systèmes de télémétrie avec suppression de porteuse sont en effet sujets à des décalages de demi-période ; le flux des données codées est alors complémenté. Si un système à

suppression de porteuse était utilisé avec une modulation NRZ-L, un décalage d'une demi-période (qui correspond à une inversion du flux de données) pourrait facilement détruire de grands blocs de données. Avec la modulation NRZ-M, l'inversion entraînerait seulement des erreurs isolées. De plus, si la chaîne de codage comprend un code de bloc (dans notre cas un code de Reed-Solomon), ces erreurs isolées pourront être facilement corrigées par le décodeur de bloc.

Des simulations ont montré [5] que la conversion NRZ-L en NRZ-M engendrait moins de dégradation (du point de vue performance pour un canal gaussien) lorsqu'elle était introduite entre le codeur Reed-Solomon et le codeur convolutionnel plutôt qu'après le codeur convolutionnel. L'utilisateur de la chaîne de codage a le choix de valider ou non la conversion grâce à un interrupteur en face avant.

#### 4. CODEUR CONVOLUTIONNEL (7, 1/2)

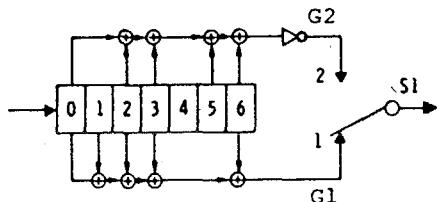

Le code convolutionnel recommandé par le CCSDS est le code de rapport  $r = 1/2$  et de longueur de contrainte  $k = 7$ .

Les deux vecteurs choisis sont G1 et G2 tels que :

$$\begin{aligned} G1 &= 1111001 \\ G2 &= 1011011 \end{aligned}$$

L'état du codeur est représenté par les 6 premiers bits du registre à décalage. Pour chaque bit d'information d'entrée, deux symboles sont générés après l'accomplissement d'un cycle de S1 : position n°1, position n°2. L'inversion d'un des symboles de sortie (G2) permet de garantir suffisamment de transitions dans le train de bits-symboles en sortie pour que la synchronisation de bit en réception puisse s'effectuer dans le cas d'états constants à l'entrée du codeur (tout à "0" ou tout à "1").

Contrairement au code de Reed-Solomon, le code convolutionnel n'est pas systématique, aucune sortie S1 ou S2 n'est identique à la séquence d'entrée du codeur.

Pour s'assurer du bon fonctionnement du codeur, un dispositif d'autotest, que l'utilisateur a la possibilité d'activer à la mise sous tension ou entre chaque séquence de codage a été incorporée. Le principe de ce dispositif consiste à injecter une séquence finie de bits à l'entrée du codeur convolutionnel puis à comparer simultanément les états des symboles de sortie du codeur à ceux d'une mémoire PROM contenant la même séquence après codage. Toute divergence dans la comparaison est indiquée à l'utilisateur à l'aide d'un voyant disposé en face avant.

Un interrupteur sur la face avant permet en outre d'utiliser soit un codage convolutionnel seul, soit un codage concaténé.

#### 5. DISPOSITIFS D'INTRODUCTION D'ERREURS

Le codeur de Reed-Solomon sera principalement utilisé pour le test des décodeurs. Il nous a alors paru intéressant de concevoir un dispositif optionnel, situé en aval du codeur permettant d'introduire des erreurs numériques dans le train de bits série obtenu après le codage de Reed-Solomon afin de contrôler le fonctionnement et les performances du décodeur de Reed-Solomon. La perturbation affectant un canal de transmission de télémesure spatiale s'effectue généralement par introduction d'un bruit blanc gaussien. Deux dispositifs plus originaux ont été mis en œuvre, le premier permettant d'introduire des erreurs numériques connues à des emplacements déterminés dans le train de bits, le second produisant le même type d'erreurs que celui engendré lors du décodage du code convolutionnel par l'algorithme de Viterbi (génération d'erreurs par "paquets") [2], [8].

Des commandes en face avant permettent de générer l'un ou l'autre de ces types d'erreurs ou de ne pas introduire d'erreurs en sortie.

Dans le premier cas, l'utilisateur indique par l'intermédiaire d'un clavier les adresses, les erreurs et le nombre d'erreurs dans le bloc codé Reed-Solomon (le nombre d'erreurs ne doit pas être supérieur à  $32 \times I$ ).

Dans le second cas, l'utilisateur peut afficher directement la valeur du rapport signal sur bruit du canal. Un générateur m séquence permet dans ce cas de simuler des erreurs par "paquets" ayant des caractéristiques sensiblement identiques à celles générées par le décodage de Viterbi.

#### 6. IMPLANTATION DE LA CHAÎNE DE CODAGE CANAL

L'ensemble de la chaîne se présente sous la forme d'un tiroir de largeur standard 19 et de profondeur 360 mm. Il est équipé d'oreilles de fixation permettant un montage en baie. Les commandes et les réglages sont disposés sur la face avant de l'appareil, les prises d'entrées et de sorties sur la face arrière. L'appareil est raccordé du point de vue électrique au secteur 220 V à travers un filtre secteur. L'alimentation en basse tension (+5V, 10A ; 15V, 1A) est assurée par une alimentation à découpage.

La technologie utilisée est une logique à circuits intégrés standards TTL et CMOS. Les circuits intégrés sont montés sur supports "tulipe" et sur cartes à wrapper du format simple Europe, de dimension 100 x 220.

La chaîne est constituée de 8 cartes = 4 cartes pour le codeur de Reed-Solomon, la conversion NRZ-L en M étant implantée sur l'une d'elles (soit 162 circuits), une carte pour le codeur convolutionnel (soit 9 circuits pour le codeur et 14 circuits pour l'autotest), 3 cartes pour le dispositif d'introduction d'erreur dont une carte microprocesseur (soit 138 circuits). Les cartes supportées par un panier de base sont connectées soit à une carte fond de panier en circuit imprimé, soit entre elles par des câbles plats.

#### 7. CONCLUSION

L'objet essentiel de cet article est la description du passage de la théorie des codes à une application technologiquement performante pour des débits élevés (au delà du Mbits/s), dans le cadre de la standardisation internationale des données spatiales. Il est important de noter que le codage par logiciel sur mini-ordinateurs ne permet pas d'espérer des débits de plus de quelques 10 kbits/s.

#### REFERENCES

Chaîne de codage par matériel

Outre son utilisation pour le test des décodeurs, cette chaîne pourrait également servir de base pour le développement de codeurs intégrés et embarqués.

- [1] Recommandation for Space Data System Standards : "Telemetry Channel Coding" Blue Book - Mai 1984 - CCSDS.

- [2] R.L. Miller, L.J. Deutsch, S.A. Butman "On the error statistics of Viterbi decoding and the performance of concatenated codes" JPL Publication 81-9 - September 1, 1981.

- [3] J.P. Rocher "Telemesures par paquet et codage des telemesures" CNES CT/DTI/CM/TT - Janvier 1985.

- [4] C. Lambert "Etude et réalisation d'un codeur convolutionnel - Etude d'un codeur de Reed-Solomon" Rapport de stage CT/DTI/CM/TT - 1er août/31 octobre 1985.

- [5] L. Deutsch, F. Pollara, L. Swanson "Effects of NRZ-M modulation on convolutional codes Performance" Nasa code 310.30.71.83.04.

- [6] J.P. Rocher "Codage Canal Telemesure C.C.S.D.S. - Performances, Applicabilité et Considérations d'utilisation" CNES CT/DTI/CM/TT n°86/159 - Mai 1986.

- [7] M. Perlman, J.J. Lee "Reed-Solomon encoders-conventional US Berlekamp's architecture" Nasa - December 1982.

- [8] C. Lambert "Codeur de Reed-Solomon" Rapport de stage DEA AIITS au CNES CT/DTI/CM/TT - 1er avril/15 septembre 1986.

- [9] F.J. MacWilliams, N.J. Sloane "The theory of error correcting codes" North Holland Mathematical Library - 1978.